复旦大学《集成电路设计导论》第3节 设计验证教程、笔记、习题及代码资源综合指南

设计验证是集成电路(IC)设计流程中的关键环节,它确保设计在功能、时序和物理层面符合规格要求,是保证芯片正确性与可靠性的基石。本节将系统讲解设计验证的核心概念、方法、工具链,并提供相关的学习资源与实战指南。

一、 设计验证概述

1. 验证的重要性

在纳米级工艺时代,芯片复杂度呈指数增长,一次流片(Tape-out)失败的成本极其高昂(可达数百万甚至上千万美元)。设计验证的目的就是在芯片制造前,尽最大可能发现并修正所有设计错误。据统计,验证工作通常占据整个设计周期的60%-70%。

2. 验证层级与流程

验证是一个多层次、渐进的过程:

- 模块级验证:针对单个功能模块(如ALU、FIFO)进行测试。

- 子系统/芯片级验证:验证多个模块集成后的功能。

- 系统级验证:将芯片置于虚拟或真实的系统环境中进行验证。

- 物理验证:包括DRC(设计规则检查)、LVS(版图与电路图一致性检查)、ERC(电气规则检查)等。

主要流程包括:制定验证计划、搭建测试平台(Testbench)、编写测试用例(Testcase)、执行仿真、分析结果并覆盖率(Coverage)评估。

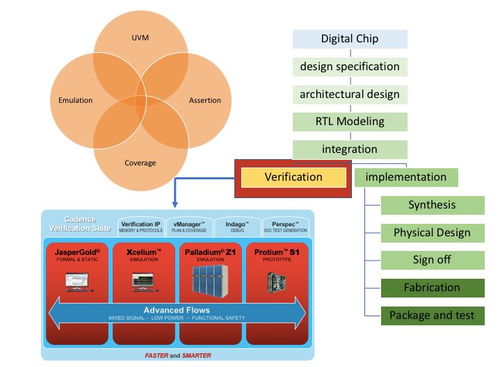

二、 主要验证方法学

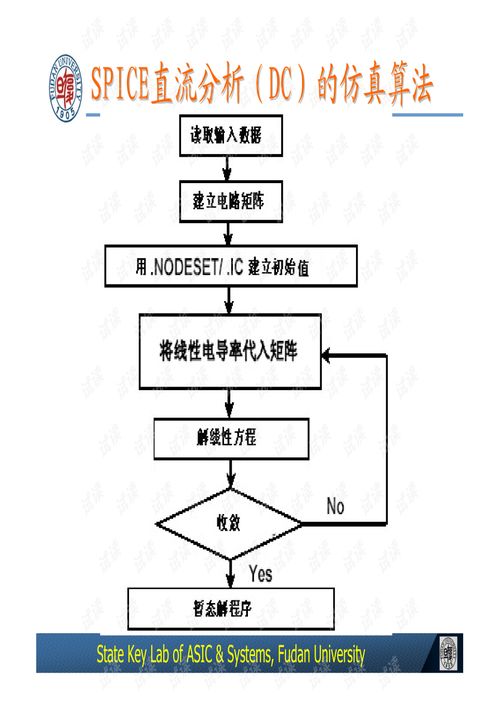

1. 动态仿真(Simulation)

- 数字仿真:使用EDA工具(如VCS, NC-Verilog, ModelSim)在软件环境中模拟电路行为。测试平台通常用SystemVerilog或UVM(通用验证方法学)搭建。

- 模拟/混合信号仿真:使用SPICE、Spectre等工具进行晶体管级仿真,精度高但速度慢。

2. 静态验证(Static Checking)

- 形式验证(Formal Verification):使用数学方法“证明”设计在某些属性上是否正确,无需测试向量。适用于控制密集型模块。

- 静态时序分析(STA):在提取寄生参数后,对设计进行全面的时序检查,确保在所有角落(Corner)下都满足时序要求。

- 等价性检查(LEC):验证综合后网表或修改后网表与原始RTL功能是否等价。

3. 硬件加速与原型验证

- 硬件仿真(Emulation):使用FPGA阵列或专用硬件仿真器,速度比软件仿真快数个数量级,适合系统级验证。

- FPGA原型验证:将设计移植到FPGA上进行实速验证,便于早期软件开发与系统集成。

三、 验证语言与平台搭建

1. 主流语言

- SystemVerilog:当前数字验证的事实标准,集成了面向对象、约束随机、断言等高级特性。

- UVM:基于SystemVerilog的类库和方法学,提供了可重用、标准化的验证平台框架。

- Python/Perl/Tcl:广泛用于编写验证脚本、结果分析和流程自动化。

2. 测试平台基本组件

一个典型的UVM测试平台包含:

- Test:顶层测试类,用于配置环境并启动测试。

- Environment:包含多个可重用的组件。

- Agent:包含驱动器(Driver)、监视器(Monitor)和序列器(Sequencer),负责接口级的激励生成与监测。

- Scoreboard:用于检查设计输出是否正确(参考模型比对)。

- Coverage Collector:收集功能覆盖率和代码覆盖率。

四、 教程、笔记与习题实战指南

1. 理论学习要点

- 深入理解验证计划、测试用例、断言、覆盖率的定义与制定方法。

- 掌握SystemVerilog的关键特性:类、随机化、约束、接口、断言(SVA)。

- 理解UVM的相位机制、配置机制、工厂模式及消息服务。

2. 习题与项目实践

- 基础习题:针对简单模块(如计数器、状态机)编写直接测试向量和SystemVerilog断言。

- 进阶项目:为一个稍复杂的IP(如UART、SPI控制器或AXI互联模块)搭建完整的UVM验证环境。要求包括:

- 编写验证计划。

- 搭建分层测试平台。

- 实现约束随机测试。

- 集成功能覆盖与代码覆盖。

- 编写回归测试脚本。

五、 代码类资源与获取建议

关于CSDN等平台的资源下载提示:

在CSDN、GitHub、OpenCores等平台,可以找到丰富的学习资源,包括:

- 参考代码:UVM验证平台模板、常见接口(APB, AHB, AXI)的验证组件、典型IP的验证环境。

- 项目实例:从简单到完整的小型SoC验证示例。

- 脚本工具:用于覆盖率合并、回归测试管理的Perl/Python脚本。

使用建议与注意事项:

1. 甄别质量:下载代码时,注意查看上传者信誉、代码更新日期和用户评价,优先选择结构清晰、注释完整的项目。

2. 理解而非复制:核心目标是学习代码结构和设计模式。务必逐行理解,并尝试修改、扩展功能。

3. 知识产权:注意资源的开源协议(如Apache, MIT),尊重原作者版权,谨慎用于商业项目。

4. 结合官方文档:最权威的资料永远是EDA厂商(Synopsys, Cadence, Siemens EDA)的官方工具手册和UVM官方标准文档。

六、

设计验证是一门理论与实践紧密结合的工程学科。掌握它需要:

- 坚实的理论基础:理解验证方法学与流程。

- 熟练的工具使用:掌握主流仿真、调试、覆盖率分析工具。

- 大量的编码实践:通过阅读优秀代码和亲手搭建验证平台来积累经验。

- 系统性的思维:从制定计划到覆盖率闭环,具备完整的项目把控能力。

建议学习者以一个小型但完整的设计验证项目为主线,将本节所述的理论、方法和资源贯穿起来,在实践中不断深化理解,从而真正掌握集成电路设计验证这项至关重要的技能。

如若转载,请注明出处:http://www.yehongjy.com/product/84.html

更新时间:2026-04-18 16:43:21