成功率和可靠性驱动的纳米尺度集成电路设计方法学

随着半导体工艺节点持续向纳米尺度演进,集成电路设计面临着前所未有的挑战。传统的、以性能和面积为单一核心导向的设计范式,在深亚微米及以下节点已显得捉襟见肘。工艺偏差、量子隧穿效应、电源电压波动、热效应以及日益加剧的软错误率等问题,严重威胁着芯片的功能正确性、性能稳定性和长期可靠性。因此,一种以“成功率和可靠性”为双重核心驱动力的新型设计方法学应运而生,成为纳米尺度集成电路设计的必然选择。

一、 核心挑战:从确定性到概率性设计的转变

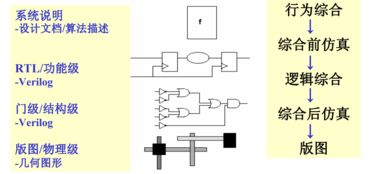

在成熟工艺节点,设计参数(如延迟、功耗)通常被认为在可控范围内呈确定性分布。进入纳米尺度后,原子级的工艺波动(如栅氧厚度、掺杂浓度、线宽边缘粗糙度)导致晶体管和互连的特性呈现显著的空间(同一芯片不同位置)和时间(同一晶体管不同时间)随机性。这使得芯片的性能、功耗乃至功能都变得具有概率性特征。设计目标不再是追求一个绝对的最优值,而是在给定的工艺扰动下,最大化芯片能够满足所有规格(功能、时序、功耗)的概率,即“首次硅成功率”(First Silicon Success Rate)和整个生命周期内的“可靠性”(Reliability)。

二、 方法学支柱:预测、建模与协同优化

成功率和可靠性驱动的方法学建立在三大支柱之上:

- 精准的统计建模与仿真:这是方法学的基石。需要建立能够精确刻画工艺波动、电压噪声、温度变化以及老化效应(如偏置温度不稳定性BTI、热载流子注入HCI)的统计模型。这些模型被集成到设计流程的各个阶段,从电路级仿真(如蒙特卡洛分析)到静态时序分析(采用统计静态时序分析SSTA),再到物理设计,确保设计决策基于对变异性的全面评估。

- 设计阶段的可靠性内建(Design-for-Reliability, DfR):将可靠性考量从“事后补救”前置到“主动设计”。这包括:

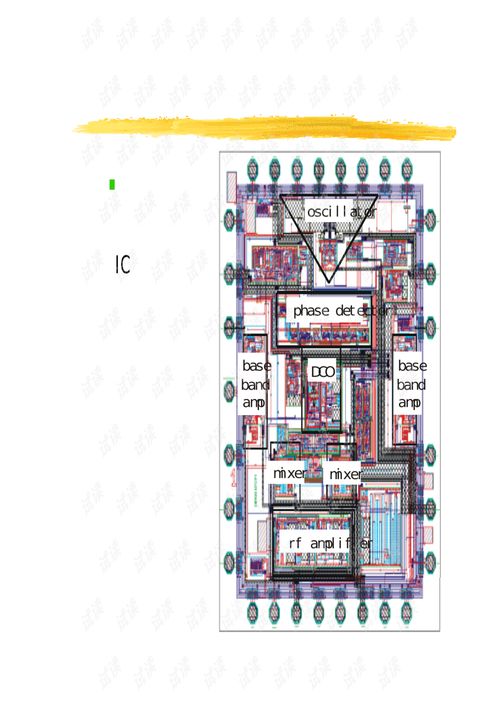

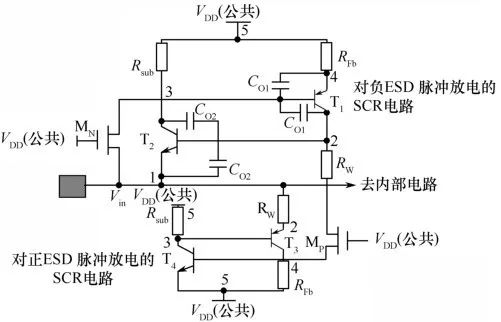

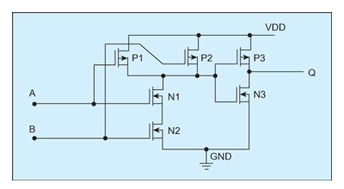

- 抗变异设计:采用电路技术(如使用反馈结构、提高器件尺寸以降低相对波动影响)、版图技术(如共同质心布局、添加冗余通孔)来抑制工艺波动的影响。

- 容错设计:对于无法完全消除的软错误(如宇宙射线引起的单粒子翻转),在关键路径和存储单元引入纠错码(ECC)、三模冗余(TMR)或自定时电路等容错机制。

- 老化感知设计:在设计阶段预测电路在生命周期内的性能退化,并通过留出时序裕量(老化防护带)、采用老化不敏感的电路结构或动态电压频率调节(DVFS)来补偿。

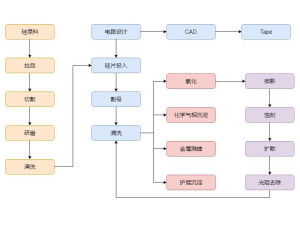

- 跨层次、跨领域的协同分析与优化:打破传统设计流程中前端(逻辑设计)与后端(物理设计)、数字与模拟、芯片与封装/系统的壁垒。实现从系统架构、微结构、逻辑设计、物理实现到制造测试的垂直整合与迭代优化。例如,系统架构可以选择冗余线程或可降级模式来容忍底层硬件的偶发错误;物理设计工具需要以统计良率和可靠性为优化目标,而不仅仅是线长和时序。

三、 关键技术与工具演进

机器学习辅助的建模与优化:利用机器学习技术从海量制造和测试数据中学习并预测工艺-设计-可靠性之间的复杂非线性关系,加速统计模型的构建,并智能探索设计空间,找到高鲁棒性的设计方案。

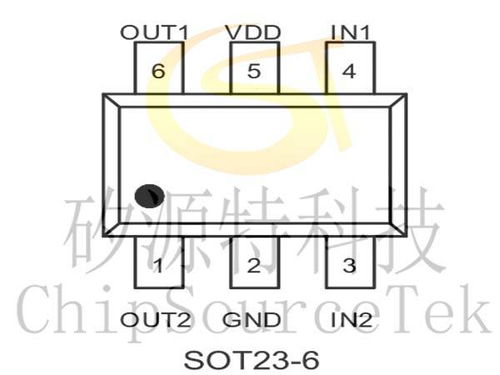

硅后调谐与自适应系统:承认纳米尺度下完全依靠设计前预测的局限性,在芯片中嵌入传感器(监测温度、电压、延迟等)和调节机制(如可调体偏置、自适应时钟分配)。芯片能够在运行时根据实际工作条件和老化状态进行动态调整,始终将性能与可靠性维持在最优区间。

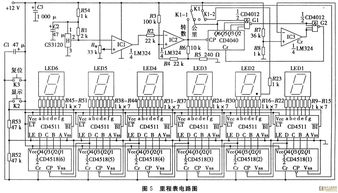

* 电子设计自动化(EDA)工具的革命:EDA工具链需要全面升级,支持从RTL到GDSII的全流程统计分析与优化。工具需要具备处理大规模统计模型的能力,并提供以良率和可靠性为度量的设计收敛指导。

四、 结论与展望

成功率和可靠性驱动的设计方法学,标志着集成电路设计从追求“理想性能”向保障“实际可用”的深刻转变。它不再将工艺波动和可靠性衰减视为需要克服的“敌人”,而是作为设计必须理解和驾驭的“内在属性”。随着工艺向3nm及以下节点、三维集成和新兴器件(如碳纳米管、二维材料)发展,变异性和可靠性挑战将更加严峻。这一方法学将与异构集成、存算一体、近似计算等新兴架构深度融合,通过更智能、更自适应、更协同的设计手段,为后摩尔时代持续释放集成电路的性能潜力,并确保其在从消费电子到自动驾驶、航空航天等关键任务应用中稳定可靠地运行。这不仅是技术路径的演进,更是设计哲学的一次重要革新。

如若转载,请注明出处:http://www.yehongjy.com/product/62.html

更新时间:2026-04-14 14:51:13