CMOS开关电路设计 从理论到实践的论坛交流热点

在当今快速发展的半导体行业中,CMOS开关电路设计作为连接数字与模拟领域的关键技术,一直是电子工程师和IC设计者关注的焦点。无论是专注于高性能模拟开关、低功耗数字切换,还是混合信号系统的集成,相关设计挑战与解决方案的讨论在各大专业论坛中始终保持着极高的热度。

以EETOP、创芯网等为代表的集成电路设计论坛,已成为全球及中国半导体从业者不可或缺的知识分享与问题解答平台。在这些论坛的“模拟电路设计”、“数字电路设计”或“混合信号设计”板块中,CMOS开关电路的相关帖子层出不穷。讨论内容广泛而深入,涵盖基础理论与高级应用。

一、 核心设计挑战与论坛热议话题

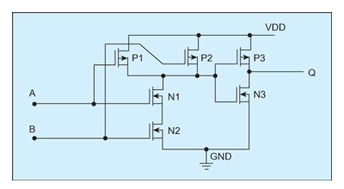

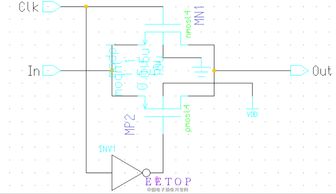

- 导通电阻(Ron)与线性度:这是模拟开关设计的核心。论坛中常探讨如何通过晶体管尺寸、布局优化以及创新架构(如传输门结构)来降低Ron并改善其随输入电压的变化,以满足精密信号路径的要求。

- 电荷注入与时钟馈通:这些非理想效应会引入误差,尤其在采样保持电路和精密数据采集系统中。资深工程师们经常分享SPICE仿真技巧、版图匹配技术以及电路补偿方法,以最小化这些效应的影响。

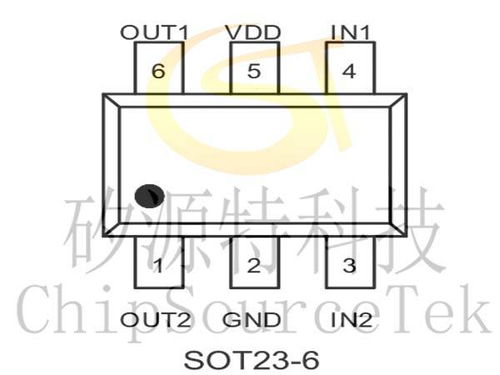

- 速度与带宽:对于高频应用,开关的切换速度和关断隔离度是关键。论坛帖子会深入分析寄生电容的影响、驱动电路的设计,以及深亚微米工艺下如何权衡速度、功耗与面积。

- 功耗与电源管理:在嵌入式设计和移动设备中,低功耗至关重要。关于采用低电压设计、电源域隔离和关断技术的讨论非常活跃。

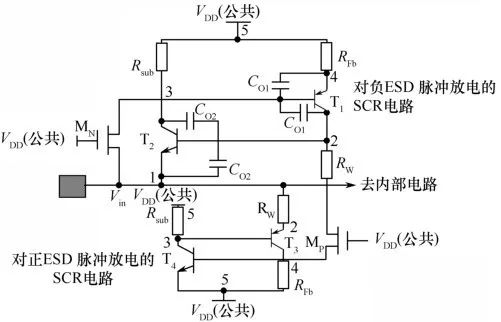

- ESD与可靠性:作为芯片的“门户”,开关电路的ESD保护设计是量产可靠性的保证。论坛中常有关于各种ESD结构(如GGNMOS、RC-Clamp)在开关电路集成中利弊的实践经验交流。

二、 设计流程与工具交流

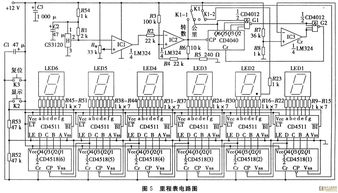

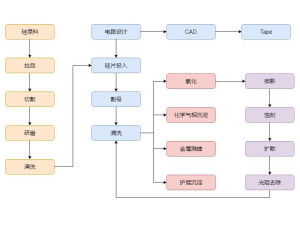

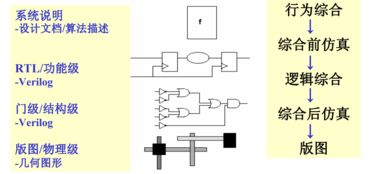

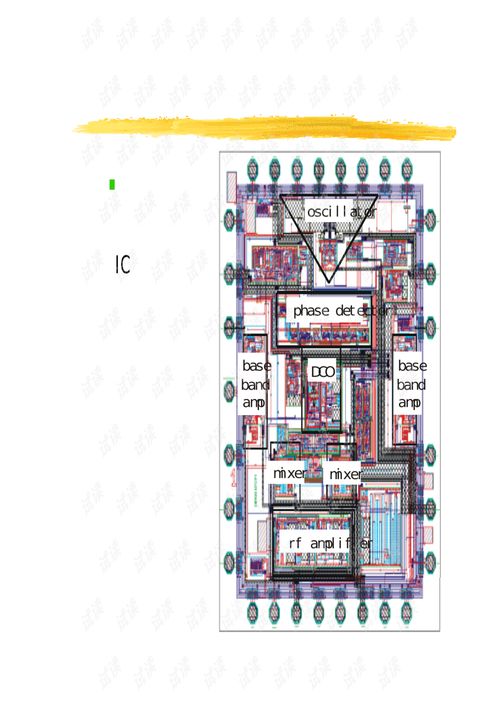

论坛不仅是问题解答的场所,也是设计方法论交流的平台。从行为级建模(Verilog-A/AMS)、电路级仿真(SPICE)、到物理版图设计,每个阶段都有大量经验分享。成员们会讨论如何设置合理的仿真边界条件,解读工艺设计套件(PDK)中的复杂模型,以及进行后仿真的注意事项。版图设计中的匹配性、隔离、闩锁效应预防等实践性极强的内容,更是图文并茂的热点。

三、 跨领域融合与趋势展望

在“集成电路设计”和“嵌入式设计”的交叉领域,CMOS开关的角色愈发重要。例如,在微控制器(MCU)的模拟前端(AFE)、可编程增益放大器(PGA)中,开关是构成配置网络的基础。论坛讨论也紧跟行业趋势,涉及先进工艺节点(如FinFET)下开关设计的新特性、用于射频(RF)领域的CMOS开关设计,以及面向物联网(IoT)传感器的超低泄漏开关方案。

EETOP、创芯网等电子工程师论坛构建了一个充满活力的技术生态系统。无论是初入行的新手寻找学习路径,还是资深专家探讨前沿难题,关于CMOS开关电路设计的交流都在持续推动着技术的进步与实践经验的沉淀。这些讨论不仅解决了具体的设计问题,更在无形中塑造着中国乃至全球半导体设计社区的集体智慧与创新能力。对于每一位投身于电子电路、半导体与集成电路设计的技术人员而言,积极参与这些论坛的讨论,无疑是保持技术敏感度、突破设计瓶颈的宝贵途径。

如若转载,请注明出处:http://www.yehongjy.com/product/56.html

更新时间:2026-04-14 15:03:05